Xilinx FPGA: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| (3 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

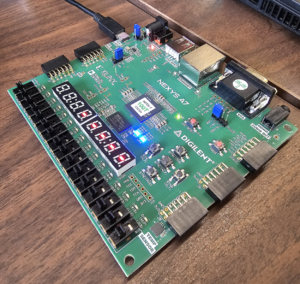

[[File:Picture of Digilent NEXYS A7.png|thumb]] | [[File:Picture of Digilent NEXYS A7.png|thumb]] | ||

I am using [https://digilent.com/shop/nexys-a7-fpga-trainer-board-recommended-for-ece-curriculum/ Digilent NEXYS A7 FPGA learning board]. It uses a Xilinx Artix®-7 FPGA. Xilinx is now under AMD. | I am using [https://digilent.com/shop/nexys-a7-fpga-trainer-board-recommended-for-ece-curriculum/ Digilent NEXYS A7 FPGA learning board]. It uses a Xilinx Artix®-7 FPGA. Xilinx is now under AMD. | ||

{|class='wikitable' | |||

| FPGA || XC7A100T-1CSG324C | |||

|- | |||

| Logic Slices || 15850 ( 1 Logic Slices = 4 Logic cell) | |||

|- | |||

| 6-inputs Look-Up Table (LUT) || 1188 | |||

|- | |||

| Shift Register [Kb] || 594 | |||

|- | |||

| Flip-Flops || 126800 | |||

|- | |||

| Block RAM [kBit] || 4860 | |||

|- | |||

| Memory || DDR 128 [MiB] (ISSI, IS43/46DR16640C) | |||

|- | |||

| Clock || 450 MHz | |||

|} | |||

=AMD Vivado Design Suite= | =AMD Vivado Design Suite= | ||

| Line 14: | Line 32: | ||

sudo ln -s /usr/lib/x86_64-linux-gnu/libtinfo.so.6 /usr/lib/x86_64-linux-gnu/libtinfo.so.5 | sudo ln -s /usr/lib/x86_64-linux-gnu/libtinfo.so.6 /usr/lib/x86_64-linux-gnu/libtinfo.so.5 | ||

sudo ln -s /usr/lib/x86_64-linux-gnu/libncurses.so.6 /usr/lib/x86_64-linux-gnu/libncurses.so.5 | sudo ln -s /usr/lib/x86_64-linux-gnu/libncurses.so.6 /usr/lib/x86_64-linux-gnu/libncurses.so.5 | ||

=== install the Cable Driver === | |||

In Linux, the driver needs to be manually install. | |||

go to the Vivado install directory | |||

cd <Vivado Install>/data/xicom/cable_drivers/lin64/install_script/install_drivers/ | |||

./install_drivers | |||

=== Run === | |||

my installation is | |||

>cd /tools/Xilinx/Vivado/2024.1 | |||

>source settings64.sh | |||

>vivado | |||

= A simple program = | |||

A youtube video '''5 - End-to-End FPGA Project on the Nexys A7''' by Anas Salah Eddin is very good introduction. | |||

= Reset the board = | |||

Press the PROG red button | |||

Latest revision as of 14:07, 15 November 2024

I am using Digilent NEXYS A7 FPGA learning board. It uses a Xilinx Artix®-7 FPGA. Xilinx is now under AMD.

| FPGA | XC7A100T-1CSG324C |

| Logic Slices | 15850 ( 1 Logic Slices = 4 Logic cell) |

| 6-inputs Look-Up Table (LUT) | 1188 |

| Shift Register [Kb] | 594 |

| Flip-Flops | 126800 |

| Block RAM [kBit] | 4860 |

| Memory | DDR 128 [MiB] (ISSI, IS43/46DR16640C) |

| Clock | 450 MHz |

AMD Vivado Design Suite

AMD Vivado Design Suite is a software tool used to design and develop hardware circuitry for programmable devices like Field-Programmable Gate Arrays (FPGAs) and System-on- a-Chip (SoC) made by AMD.

require libraries

sudo apt install libtinfo-dev libtinfo.so.6 libncurses.so.6

the suite actually needs libtinfo5 and ncurses5. but we can cheat it by creating symbolic links

sudo ln -s /usr/lib/x86_64-linux-gnu/libtinfo.so.6 /usr/lib/x86_64-linux-gnu/libtinfo.so.5 sudo ln -s /usr/lib/x86_64-linux-gnu/libncurses.so.6 /usr/lib/x86_64-linux-gnu/libncurses.so.5

install the Cable Driver

In Linux, the driver needs to be manually install.

go to the Vivado install directory

cd <Vivado Install>/data/xicom/cable_drivers/lin64/install_script/install_drivers/ ./install_drivers

Run

my installation is

>cd /tools/Xilinx/Vivado/2024.1 >source settings64.sh >vivado

A simple program

A youtube video 5 - End-to-End FPGA Project on the Nexys A7 by Anas Salah Eddin is very good introduction.

Reset the board

Press the PROG red button