CAEN digitizer

Model

| Model | Energy resolution | Sampling rate |

|---|---|---|

| V1725 | 14-bit | 250MS/s |

| V1730 | 14-bit | 500MS/s |

| V1740 | 12-bit | 62.5 MS/s |

DPP firmware

Both V1725 and V1730 can be equipped with the PHA (pulse-height analysis) or PSD (pulse-shape decimation) firmware.

From the programming point of view, the channel registers ( < 0x1XXX ) are very different for the two firmware, but the board registers (0x8000 to 0xFFFF) are almost identical.

required library

On Linux (Ubuntu 18.04+), two CAEN libraries are required to run the digitizers.

- CAENVMELib

- CAENComm

that would be enough for running the CAEN CoMPASS.

For custom programs, an additional library is needed

- CAENDigitizer

PLL firmware

A digitizer need a proper PLL firmware to run.

If the PLL firmware is wrong (i.e. The PLL lock led is off ), you need to refresh the PLL firmware using the CAENUpgrader

The PLL file has the format of V17XX_vcxo500_refYY_pll_outZZ.rbf

where

XX is the model type,

for example 25, 25S, 30, 40

YY is the ref clock,

for the master or stand alone digitizer, 50 (= 50 MHz ) is ok. for a slave, it must be 62_5.

ZZ is the clock output,

for master or stand alone digitizer, 0 or 62_5 (= 62.5) are OK. for a master that connect to a slave, it must be 62_5. for a slave, that connect to an other slave, it must be 62_5

Reading the bin file from CAEN CoMPASS

The CoMPASS can output *.bin data. The beginning of the file is a 2 bytes header. It must be in the form of 0xCAEx, where x indicate the energy format and waveform existence. After that,

| block | bytes |

|---|---|

| Board | 2 |

| Channel | 2 |

| Timestamp | 8 |

| Energy | [x == 1, 2], [x == 2, 8], [x == 3, 10], [x == 4, 2] |

| Flags | 4 |

| Waveform code | 1 |

| number of samples | 4 |

| trace ... | 2 * (number of samples) |

If x < 8, there is no waveform.

A BinReader class can be found in here.

Data structure, Read-out, and buffer size

In the CAENDigitizer.h, the CAEN_DGTZ_READDATA() will read the buffer of the digitizer. For a single call of the function, ONE aggregate of data is read from the buffer and clear.

The number of events for an aggregate is set by register 0x1034. When set to zero, the digitizer (mysteriously) auto-set.

The data structure started with 4 words ( 1 word = 32 bits).

FSUDAQ

https://fsunuc.physics.fsu.edu/git/rtang/FSUDAQ

The (idea of the) FSU DAQ is based on the BoxScore(code of BoxScore). The core is the digitizer class that directly controls and reads out the CAEN digitizer. The GUI of the DAQ uses CERN ROOT GUI elements.

The Goals for the DAQ are:

- support V1725, V1730, V1740 digitizers

- multi-thread readout and real-time time sorting (possibly events building)

- extendable to other digitizers and functionalities

- user-friendly (full GUI, limited terminal output)

- easy to maintain (avoid abstract coding and entirely objective programming)

- for Ubuntu 22.04 or equivalent

- binary output or root tree output

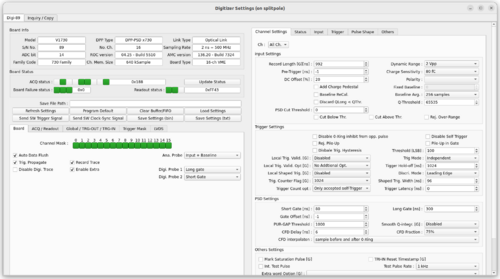

FSUDAQ (using Qt6)

The FSUDAQ GUI uses CERN ROOT Qt, which is based on Qt4. A new GUI is being made using Qt6. The FSUDAQ(Qt6) is very similar to te SOLARIS DAQ.

https://fsunuc.physics.fsu.edu/git/rtang/FSUDAQ_Qt6

The Digitizer Class

The Digitizer class is ClassDigitizer.h/C. The class controls the digitizer by manipulating the register. And various types of digitizers are different by the registers. Thus, the class can control different types of digitizers without modification. The digitizer classes stores the connection, and board information, and a copy of the register. It provides an interface to better control the digitizer, for example, manipulate the bits for the control bit.

The digitizer classes directly write/read the registers in the digitizer. The advantage is complete control of the hardware and simplified the program that only 3 pieces are needed:

- WriteRegister()

- ReadRegister()

- Table of Register Address

- Load (Save) register setting from (to) a binary file

The drawback is that, the buffer size must be calculated (a lazy man method is assign 10 MB for the buffer?).

Register Address and Setting Binary File

The registers < 0x8000 are channel settings. For example, 0x1nXX is for channel-n, or 0x80XX is for writing to all channels. The registers >= 0x8000 are board settings.

For all types of digitizers, the register > 0x8000 registers are the same and have the same meaning.

Because the 2n and 2n+1 channels are paired ( like shared same memory ). There are some registers also paired. for example, the record length is the same for any paired channels, once the record length is set for any one of the paired channels, the record length of the other channel is also set.

A Setting uses 4 bytes (unsigned int) to store 32 bits of each register value. Using an array of size 2048 can store all register settings, which is only 8192 bytes. The following table shows the conversion.

| Address Range | Comment | Setting Index | Example |

|---|---|---|---|

| 0x1000 - 0x1FFF | Channel Setting | 0x1XXX / 4 | 0x1020 -> 1032 |

| 0x8000 - 0x81FF | Board Setting | 0x8XXX & 0x0FFF | 0x8080 -> 32 |

| 0xEF00 - 0xEFFF | Other Board Setting | 0xEXXX & 0x0FFF | 0xEF04 -> 961 |

| 0xF000 - 0xFFFF | Read only board configuration | (0xFXXX & 0x0FFF) + 0x0200 | 0xF008 -> 520 |

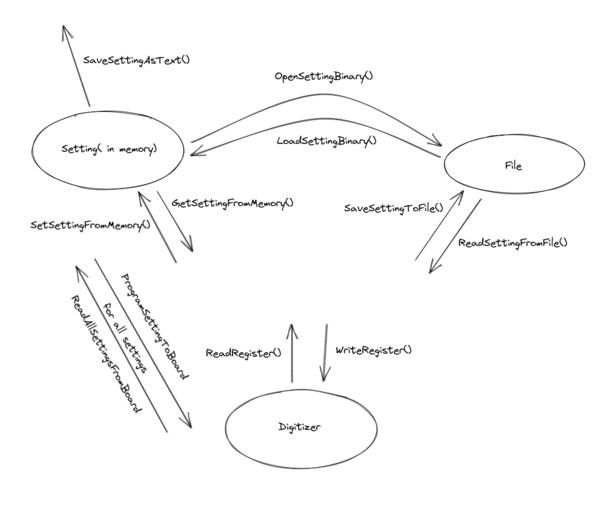

The digitizer class provides a method to convert the setting binary to a text file. The following diagram illustrates the methods between board setting, setting in memory, and setting file

Buffer Size calculation

The data stored in the digitizer can be retrieved using

CAEN_DGTZ_ReadData(int handle, CAEN_DGTZ_ReadMode_t mode, char *buffer, uint32_t *bufferSize);

typedef enum {

CAEN_DGTZ_SLAVE_TERMINATED_READOUT_MBLT = 0,

CAEN_DGTZ_SLAVE_TERMINATED_READOUT_2eVME = 1,

CAEN_DGTZ_SLAVE_TERMINATED_READOUT_2eSST = 2,

CAEN_DGTZ_POLLING_MBLT = 3,

CAEN_DGTZ_POLLING_2eVME = 4,

CAEN_DGTZ_POLLING_2eSST = 5,

} CAEN_DGTZ_ReadMode_t;

The data format of the buffer contains two parts: A whole chuck of the buffer can contain multiple board aggregation (depending on the value of 0xEF1C). Inside a board aggregation, there could be at most 8 Dual Channels Aggregation, depending on the channel mask. Each Dual Channels Aggregation can contain at most 511 measurements (set by 0x1n34). See the block diagrams on the

Each Board Aggregation has 4 words of header. 1 words = 4 bytes = 32 bits. Each Dual channel Aggregation has 2 words of header. after that is Ne events (0x1n34) for paired channels. In each measurement, there is 1 word of header, Sample/2 words for waveform, 1 word for Extra2 (if any), and 1 word for Energy, so total = (2 + Sample/2 + Extra), where Sample size is the Record Length = (0x1n20) * 8 ch. Extra is controlled by bit[17] of (0x8000), denote as (0x8000:17)

There is a maximum of 8 Dual Channel aggregations for 1 Board Aggregation for 16-channel digitizer. Thus, for 1 Board Aggregation, the max number of words is 4 + 8 * (n * (2 + Sample/2 + Extra)).

In Each readout, there can be more than 1 Board Aggregation (0xEF1C). The total buffer size (byte) needed is

where bit value of 0xEF1C

bit value of 0x1n34, n = paired channel ID

Channel enabled mask of the paired channel n.

bit value of 0x1n20

bit value of 0x8000, bit-17

However, this calculation is about factor 2 smaller than the CAEN's calculation in

CAEN_DGTZ_MallocReadoutBuffer(int handle, char **buffer, uint32_t *size);

The CAEN's formula for the buffer size is almost 2 times more.

Readout

The Event per Aggregation (0x1n34) are shared by the paired channels. for example, for 10 Event per Aggregation, the dual channel aggregation will only store 10 events for both paired channels.

The Maximum trigger for each dual channel is (Event per Aggregation) * (Aggregation per readout)

Also, it seems that, the maximum events in all paired channel is set by the maximum event number of the highest trigger rate channel. For example, I have 27 Hz input for channel 0,1, and 15. Although the Event per Aggregation was set to 60. the number event in the 0-1 dual channel aggregation is 27, which is the same number as the 14-15 dual channel.

Contact

Tsz Leung (Ryan) Tang mailto:rtang@fsu.edu